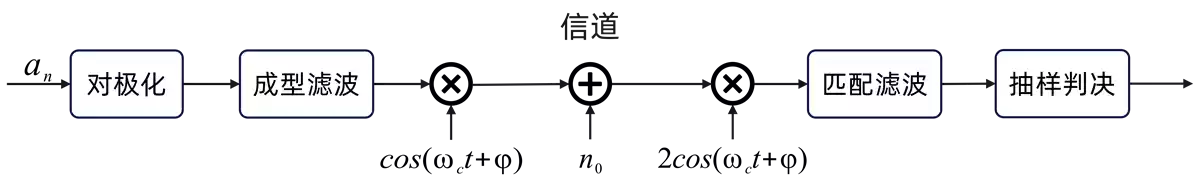

二进制相移键控(BPSK)

基础

BPSK 的时域表达式是

MATLAB 仿真

按照上图流程进行 MATLAB 仿真

调制与解调

设定参数:系统时钟频率为

1 2 3 4 5 6 7 sys_clk = 160e6 ; Rb = 5e6 ; Rs = Rb; Ts = 1 / Rs; usmp_rate = sys_clk / Rs; fc = 20e6 ; hrc = 'rrc' ;

随机生成 num 个二进制数,并对极化处理:

1 2 3 4 num = round (100000 * 10 ^ (EbNo / 10 )); b = randi([0 1 ], 1 , num); b_sign = 1 - 2 * b;

成型滤波,并去除延迟:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 switch hrc case 'rect' h = ones (1 , usmp_rate + 1 ); case 'sinc' t = -3 * pi : pi / usmp_rate : 3 * pi ; h = sinc(t); case 'rrc' beta = 0.35 ; span = 6 ; sps = usmp_rate; h = rcosdesign(beta , span, sps, 'sqrt' ); end baseband = conv(upsample(b_sign, usmp_rate), h); delay = (length (h) - 1 ) / 2 ; baseband = baseband(delay + 1 :end - delay);

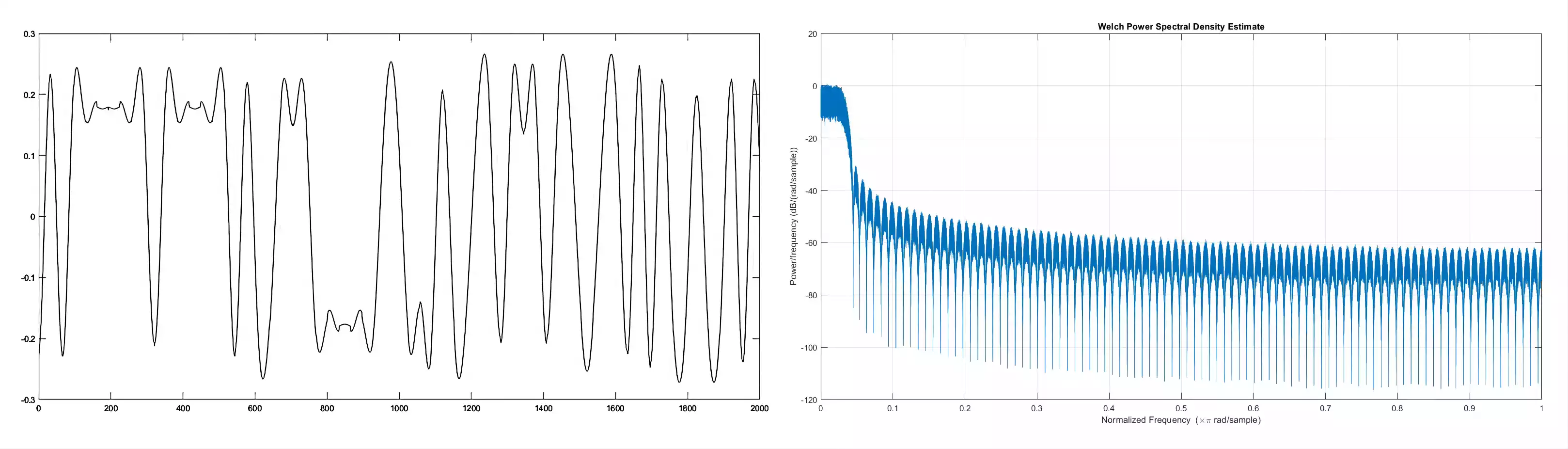

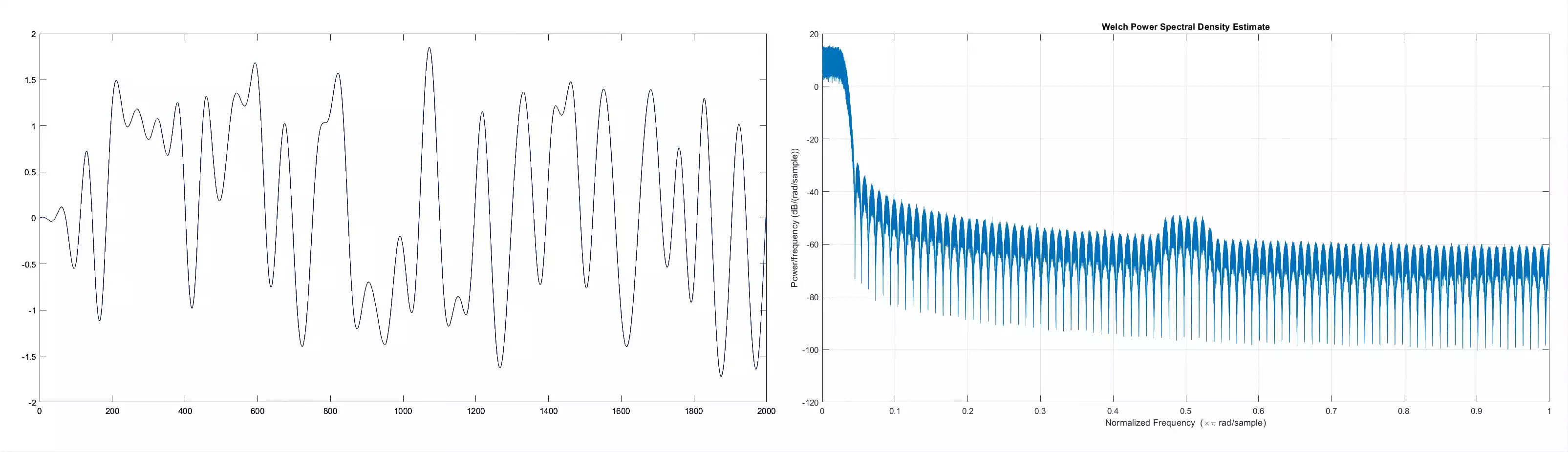

基带信号的时域波形与功率谱密度

载波调制

1 2 3 4 5 phase = 2 * pi * rand ; total_t = Ts * num; t = 0 : 1 /sys_clk : (total_t - 1 /sys_clk); carrier = cos (2 * pi * fc * t + phase); modulated_signal = baseband .* carrier;

调制信号的时域波形与功率谱密度

经过高斯白噪声信道

1 2 SNR = EbNo - 10 * log10 (usmp_rate / 2 ); noised_signal = awgn(modulated_signal, SNR, 'measured' );

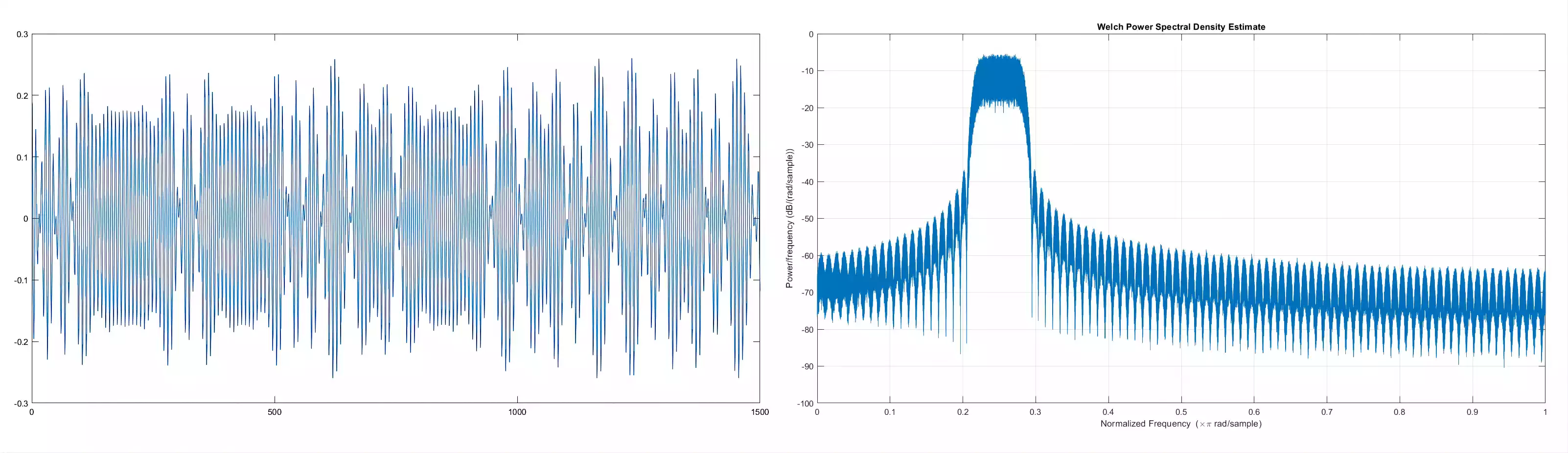

相干解调

1 2 local_carrier = 2 * carrier; received_signal = noised_signal .* local_carrier;

相干解调信号的时域波形与功率谱密度

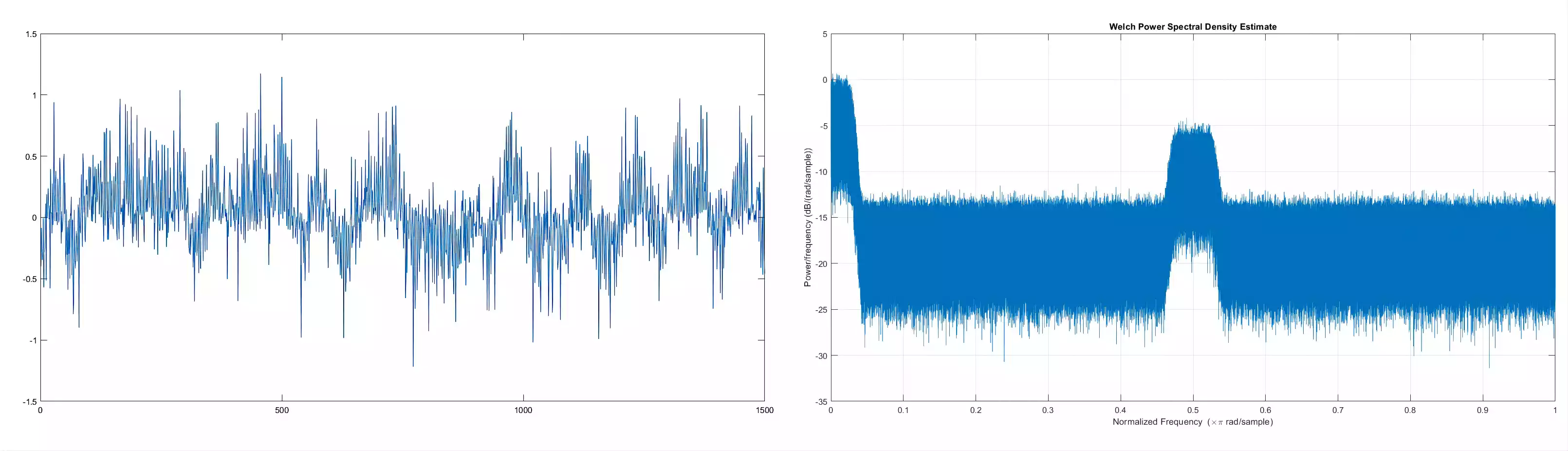

匹配滤波与抽样判决

1 2 3 4 mf_dout = conv(received_signal, fliplr (h)); delay = (length (h) - 1 ) / 2 ; decision_result = downsample(mf_dout(delay+1 :end ), usmp_rate); decision_result = decision_result(1 :num);

匹配滤波后信号的时域波形与功率谱密度

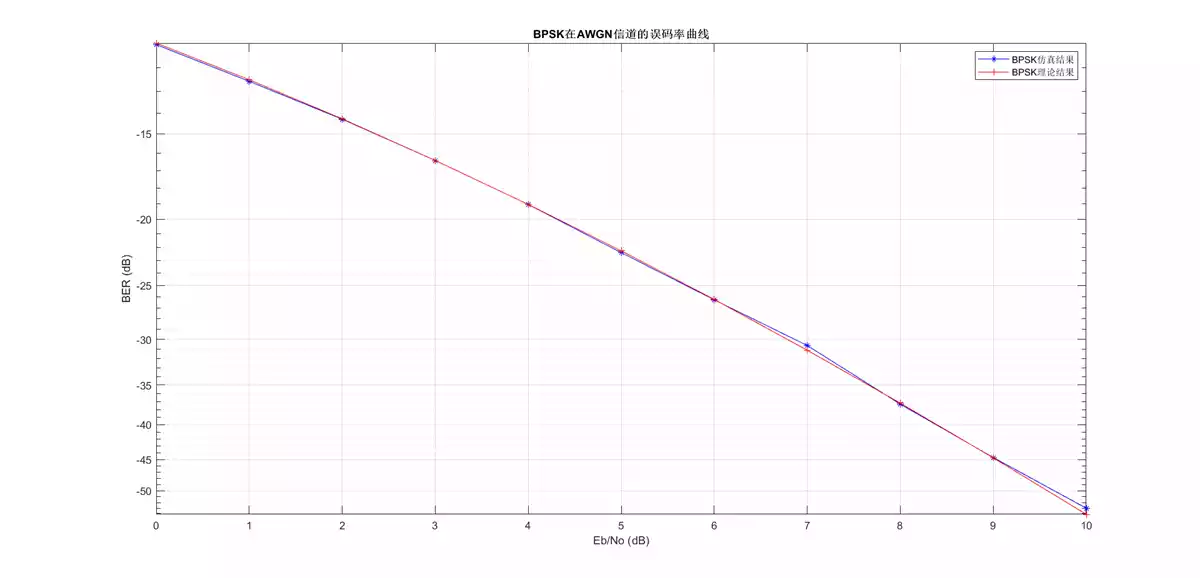

仿真结果

将仿真得到的误比特率曲线与理论误比特率曲线比较,基本重合

理论分析

载波频率对误比特率的影响

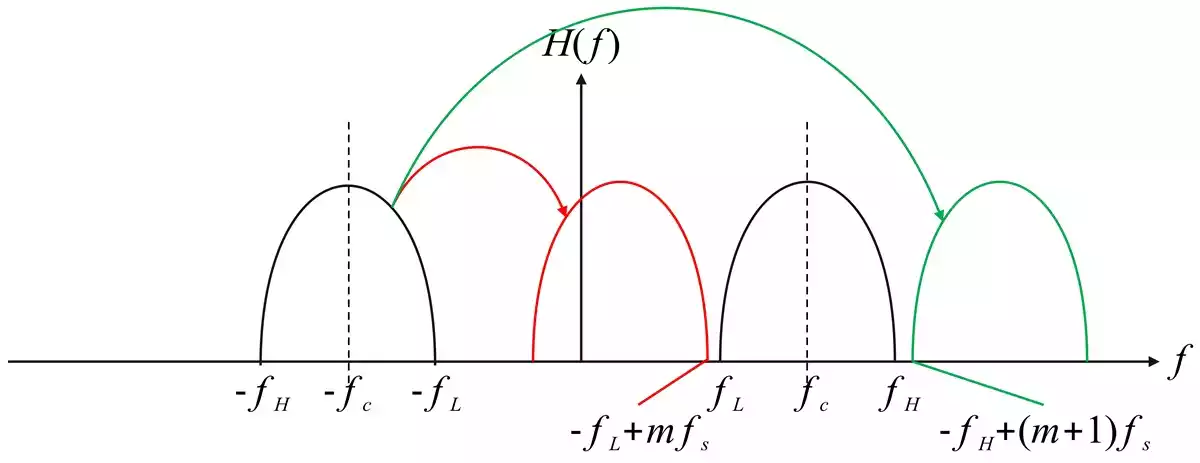

带通采样定理:

频带信号如图所示,为了保证被采样后不会发生混叠,需要满足条件:

在采样频率、码元速率一定时,由带通采样定理可以推导出载波频率 载波频率的取值范围 是

内插系数对误比特率的影响

当

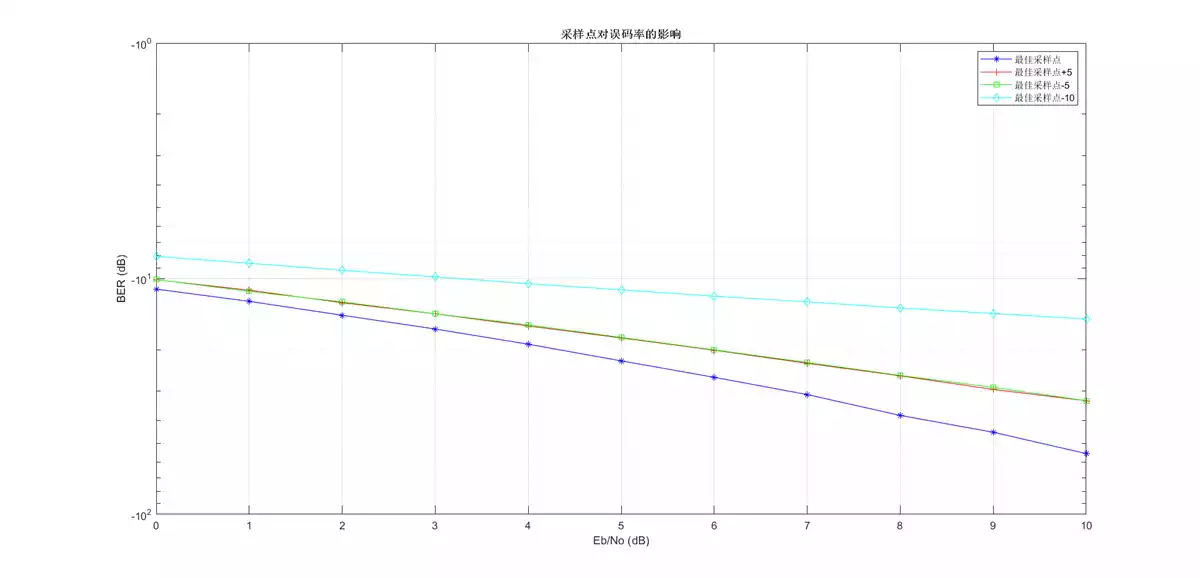

接收机采样点位置对误比特率的影响

由仿真结果可以看出,在最佳的接收机采样点处采样,误比特率最低,距离该点越远,误比特率越高。

成型滤波器对误比特率的影响

几乎无影响。

FPGA 仿真(调制)

设定参数:系统时钟频率为

1 2 3 4 5 6 7 8 9 10 11 12 13 reg [14 :0 ] counter = 15'd0 ;always @(posedge clk) begin if (!rst_n) begin counter[14 :0 ] <= 13'd0 ; end else begin counter[14 :0 ] <= counter[14 :0 ] + 13'd1 ; end end wire [9 :0 ] address;assign address[9 :0 ] = counter[14 :5 ];

由系统时钟频率和传输速率可以得到内插系数为 reg [14:0] counter,每计数 counter 的高

存储数据、成型滤波、载波调制等过程通过 IP 核实现:

存储数据

Block Memory Generator

成型滤波

FIR Compiler

生成载波

DDS Compiler

载波调制

Multiplier

生成系统时钟

Clock Wizard

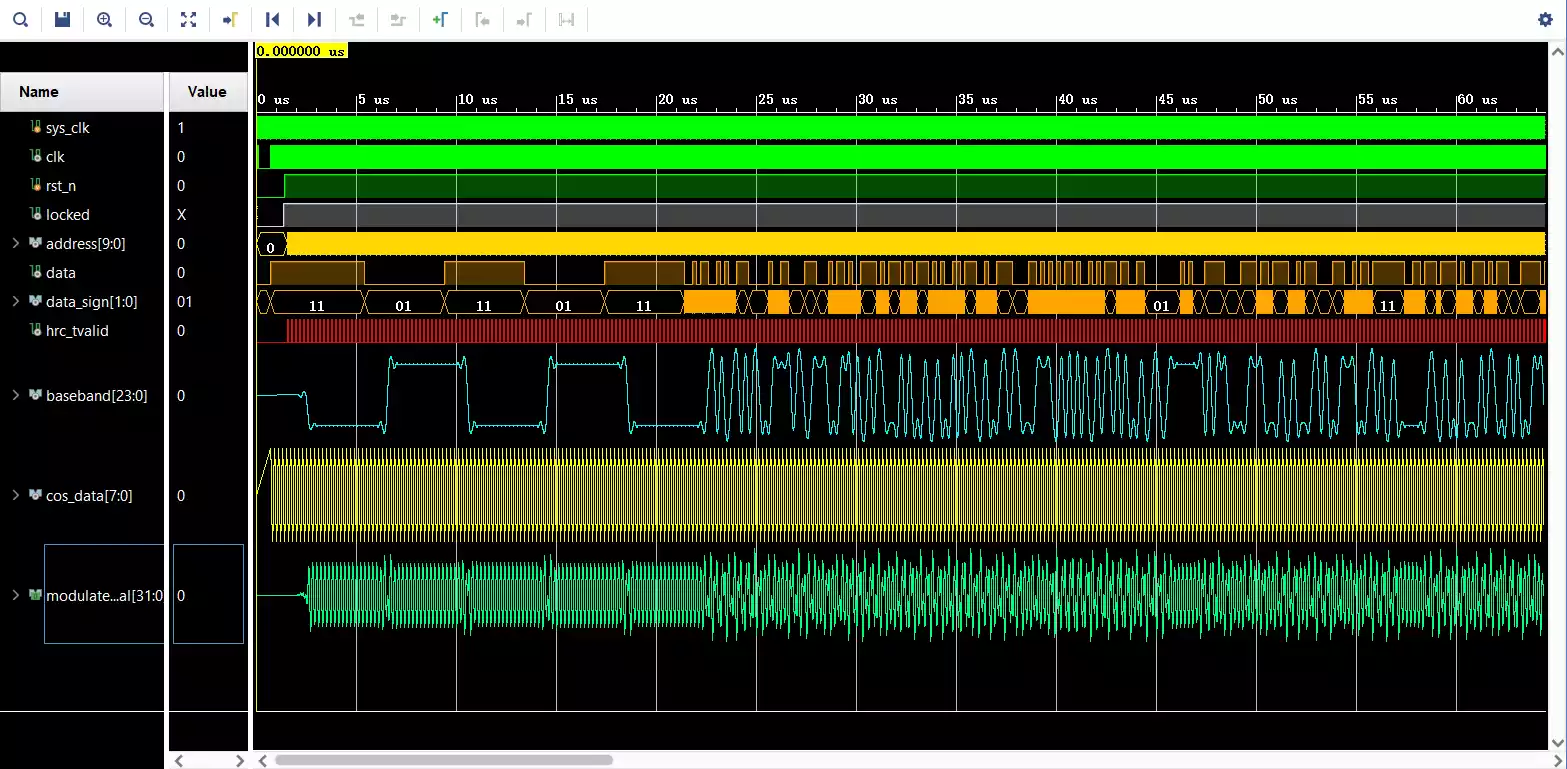

仿真波形如下图

附录

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 close all; clear; clc; tic; fs = 122.88e6 ; Rs = 3.072e6 ; Rb = Rs; Ts = 1 / Rs; N = 65536 ; t = (1 : N) / fs; usmp_rate = floor (fs / Rs); num = 5000 ; b = 1 - 2 * randi([0 1 ], 1 , num); beta = 0.1 ; span = 12 ;sps = usmp_rate; h = rcosdesign(beta , span, sps, "sqrt" ); baseband = conv(upsample(b, usmp_rate), h, "same" ); baseband = baseband(1 :N); figure ;subplot(2 , 1 , 1 ); plot (t, baseband);xlabel("Time (s)" ); ylabel("Amplitude" ); title("BPSK Baseband Signal" ); grid on; subplot(2 , 1 , 2 ); f = (-fs/2 : fs/N : fs/2 -fs/N); plot (f, 10 * log10 (abs (fftshift(fft(baseband, N)))));xlabel("Frequency (Hz)" ); ylabel("Amplitude (dB)" ); title("BPSK Baseband Spectrum" ); grid on; bpsk_baseband = baseband(1 :N); save("bpsk_baseband.mat" , "bpsk_baseband" ); toc;